# ibaFOB-R

Schnittstellenkarte für Reflective Memory

Handbuch

Ausgabe 1.0

Messsysteme für Industrie und Energie

[www.iba-ag.com](http://www.iba-ag.com)

---

## **Hersteller**

iba AG

Königswarterstraße 44

90762 Fürth

Deutschland

## **Kontakte**

|          |                                                    |

|----------|----------------------------------------------------|

| Zentrale | +49 911 97282-0                                    |

| Support  | +49 911 97282-14                                   |

| Technik  | +49 911 97282-13                                   |

| E-Mail   | iba@iba-ag.com                                     |

| Web      | <a href="http://www.iba-ag.com">www.iba-ag.com</a> |

Weitergabe sowie Vervielfältigung dieser Unterlage, Verwertung und Mitteilung ihres Inhalts sind nicht gestattet, soweit nicht ausdrücklich zugestanden. Zu widerhandlungen verpflichten zu Schadenersatz.

© iba AG 2024, alle Rechte vorbehalten.

Der Inhalt dieser Druckschrift wurde auf Übereinstimmung mit der beschriebenen Hard- und Software überprüft. Dennoch können Abweichungen nicht ausgeschlossen werden, so dass für die vollständige Übereinstimmung keine Garantie übernommen werden kann. Die Angaben in dieser Druckschrift werden jedoch regelmäßig aktualisiert. Notwendige Korrekturen sind in den nachfolgenden Auflagen enthalten oder können über das Internet heruntergeladen werden.

Die aktuelle Version liegt auf unserer Website [www.iba-ag.com](http://www.iba-ag.com) zum Download bereit.

| Version | Datum   | Revision    | Autor  | Version<br>HW/FW |

|---------|---------|-------------|--------|------------------|

| 1.0     | 08-2024 | Erstausgabe | CV, st | 1.0              |

Windows® ist eine Marke und eingetragenes Warenzeichen der Microsoft Corporation. Andere in diesem Handbuch erwähnte Produkt- und Firmennamen können Marken oder Handelsnamen der jeweiligen Eigentümer sein.

## **Zertifizierung**

Dieses Produkt ist entsprechend der europäischen Normen und Richtlinien zertifiziert. Dieses Produkt entspricht den allgemeinen Sicherheits- und Gesundheitsanforderungen.

Weitere internationale und landesübliche Normen wurden eingehalten.

---

Die Ausrüstung wurde getestet und entspricht den Grenzwerten für Digitalgeräte der Klasse A gemäß Teil 15 der FCC-Regularien (Federal Communications Commission). Diese Grenzwerte wurden geschaffen, um angemessenen Schutz gegen Störungen beim Betrieb in gewerblichen Umgebungen zu gewährleisten. Diese Ausrüstung erzeugt, verwendet und kann Hochfrequenzenergie abstrahlen und kann - falls nicht in Übereinstimmung mit der Dokumentation installiert und verwendet - Störungen der Funkkommunikation verursachen. In Wohnumgebungen kann der Betrieb dieses Geräts Funkstörungen verursachen. In diesem Fall obliegt es dem Anwender, angemessene Maßnahmen zur Beseitigung der Störung zu ergreifen.

**Inhalt**

|           |                                              |           |

|-----------|----------------------------------------------|-----------|

| <b>1</b>  | <b>Zu dieser Dokumentation .....</b>         | <b>6</b>  |

| 1.1       | Zielgruppe.....                              | 6         |

| 1.2       | Schreibweisen.....                           | 6         |

| 1.3       | Verwendete Symbole.....                      | 7         |

| <b>2</b>  | <b>Über ibaFOB-R .....</b>                   | <b>8</b>  |

| 2.1       | Eigenschaften .....                          | 9         |

| 2.2       | PCI Express-Konformität .....                | 9         |

| 2.3       | Hersteller- und Gerätekennung .....          | 9         |

| <b>3</b>  | <b>Sicherheitshinweise .....</b>             | <b>10</b> |

| 3.1       | Bestimmungsgemäßer Gebrauch .....            | 10        |

| 3.2       | Spezielle Sicherheitshinweise .....          | 10        |

| <b>4</b>  | <b>Lieferumfang.....</b>                     | <b>11</b> |

| <b>5</b>  | <b>Systemvoraussetzungen .....</b>           | <b>12</b> |

| <b>6</b>  | <b>Karte ein- und ausbauen .....</b>         | <b>13</b> |

| 6.1       | Karte einbauen .....                         | 13        |

| 6.2       | Karte ausbauen.....                          | 14        |

| <b>7</b>  | <b>Beschreibung .....</b>                    | <b>15</b> |

| 7.1       | Vorderansicht .....                          | 15        |

| 7.2       | Draufsicht .....                             | 16        |

| 7.3       | Anzeigeelemente .....                        | 16        |

| 7.4       | LWL-Verbindungen .....                       | 17        |

| <b>8</b>  | <b>Konfiguration .....</b>                   | <b>18</b> |

| 8.1       | Konfiguration Schalter S1 .....              | 18        |

| 8.2       | Konfiguration Schalter S2 .....              | 19        |

| 8.2.1     | Wichtige Hinweise vor der Installation ..... | 20        |

| <b>9</b>  | <b>Konfiguration in ibaPDA .....</b>         | <b>22</b> |

| <b>10</b> | <b>Systemintegration .....</b>               | <b>23</b> |

| 10.1      | Grundlegende Funktionen und Bedienung.....   | 23        |

| 10.2      | ibaFOB-R Hardware-Register .....             | 24        |

|           |                                          |           |

|-----------|------------------------------------------|-----------|

| 10.3      | Reflective Memory RAM auf ibaFOB-R.....  | 24        |

| 10.4      | Interrupt generieren.....                | 25        |

| 10.5      | Netzwerk Interrupts.....                 | 26        |

| 10.6      | Redundanter Übertragungsmodus .....      | 27        |

| 10.7      | Rogue Packet Removal Betriebsmodus ..... | 27        |

| 10.8      | Anforderungen an die Programmierung..... | 28        |

| 10.8.1    | PCI Configuration Register .....         | 28        |

| 10.8.2    | Local Configuration Register .....       | 37        |

| 10.8.3    | RFM Control and Status Register .....    | 41        |

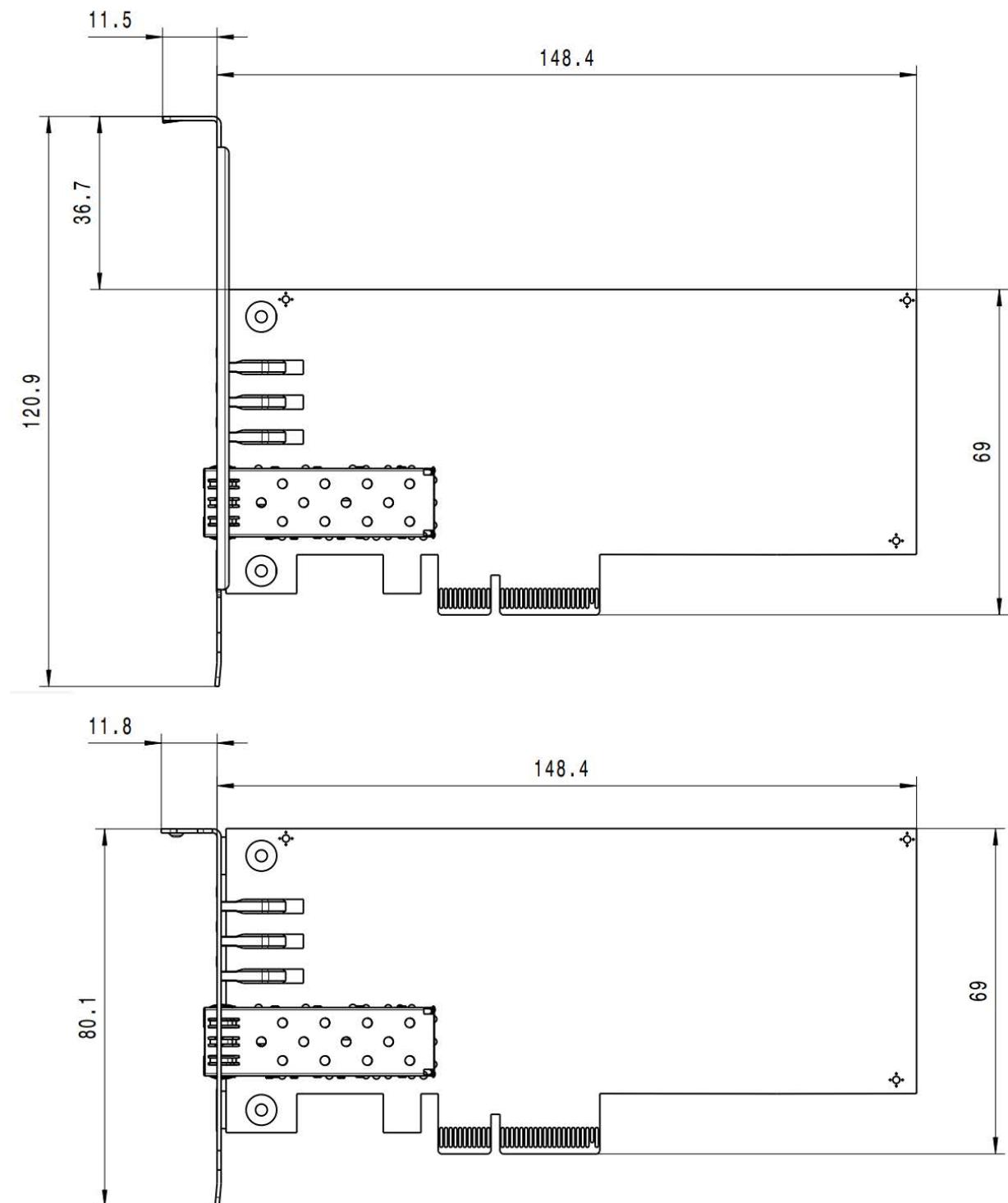

| <b>11</b> | <b>Technische Daten .....</b>            | <b>53</b> |

| 11.1      | Abmessungen .....                        | 54        |

| <b>12</b> | <b>Support und Kontakt.....</b>          | <b>55</b> |

# 1 Zu dieser Dokumentation

Diese Dokumentation beschreibt den Aufbau, die Anwendung und die Bedienung des Gerätes *ibaFOB-R*.

## 1.1 Zielgruppe

Diese Dokumentation wendet sich an ausgebildete Fachkräfte, die mit dem Umgang mit elektronischen und elektronischen Baugruppen sowie der Kommunikations- und Messtechnik vertraut sind. Als Fachkraft gilt, wer auf Grund der fachlichen Ausbildung, Kenntnisse und Erfahrungen sowie Kenntnis der einschlägigen Bestimmungen die übertragenen Arbeiten beurteilen und mögliche Gefahren erkennen kann.

## 1.2 Schreibweisen

In dieser Dokumentation werden folgende Schreibweisen verwendet:

| Aktion                              | Schreibweise                                                                                                                                  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Menübefehle                         | Menü <i>Funktionsplan</i>                                                                                                                     |

| Aufruf von Menübefehlen             | <i>Schritt 1 – Schritt 2 – Schritt 3 – Schritt x</i><br>Beispiel:<br>Wählen Sie Menü <i>Funktionsplan – Hinzufügen – Neuer Funktionsblock</i> |

| Tastaturtasten                      | <Tastenname><br>Beispiel: <Alt>; <F1>                                                                                                         |

| Tastaturtasten gleichzeitig drücken | <Tastenname> + <Tastenname><br>Beispiel: <Alt> + <Strg>                                                                                       |

| Grafische Tasten (Buttons)          | <Tastenname><br>Beispiel: <OK>; <Abbrechen>                                                                                                   |

| Dateinamen, Pfade                   | <a href="#">Dateiname, Pfad</a><br>Beispiel: <a href="#">Test.docx</a>                                                                        |

## 1.3 Verwendete Symbole

Wenn in dieser Dokumentation Sicherheitshinweise oder andere Hinweise verwendet werden, dann bedeuten diese:

---

### Gefahr!

**Wenn Sie diesen Sicherheitshinweis nicht beachten, dann droht die unmittelbare Gefahr des Todes oder der schweren Körperverletzung!**

- Beachten Sie die angegebenen Maßnahmen.

-

### Warnung!

**Wenn Sie diesen Sicherheitshinweis nicht beachten, dann droht die mögliche Gefahr des Todes oder schwerer Körperverletzung!**

- Beachten Sie die angegebenen Maßnahmen.

-

### Vorsicht!

**Wenn Sie diesen Sicherheitshinweis nicht beachten, dann droht die mögliche Gefahr der Körperverletzung oder des Sachschadens!**

- Beachten Sie die angegebenen Maßnahmen.

-

### Hinweis

Hinweis, wenn es etwas Besonderes zu beachten gibt, wie z. B. Ausnahmen von der Regel usw.

---

### Tipp

Tipp oder Beispiel als hilfreicher Hinweis oder Griff in die Trickkiste, um sich die Arbeit ein wenig zu erleichtern.

---

### Andere Dokumentation

Verweis auf ergänzende Dokumentation oder weiterführende Literatur.

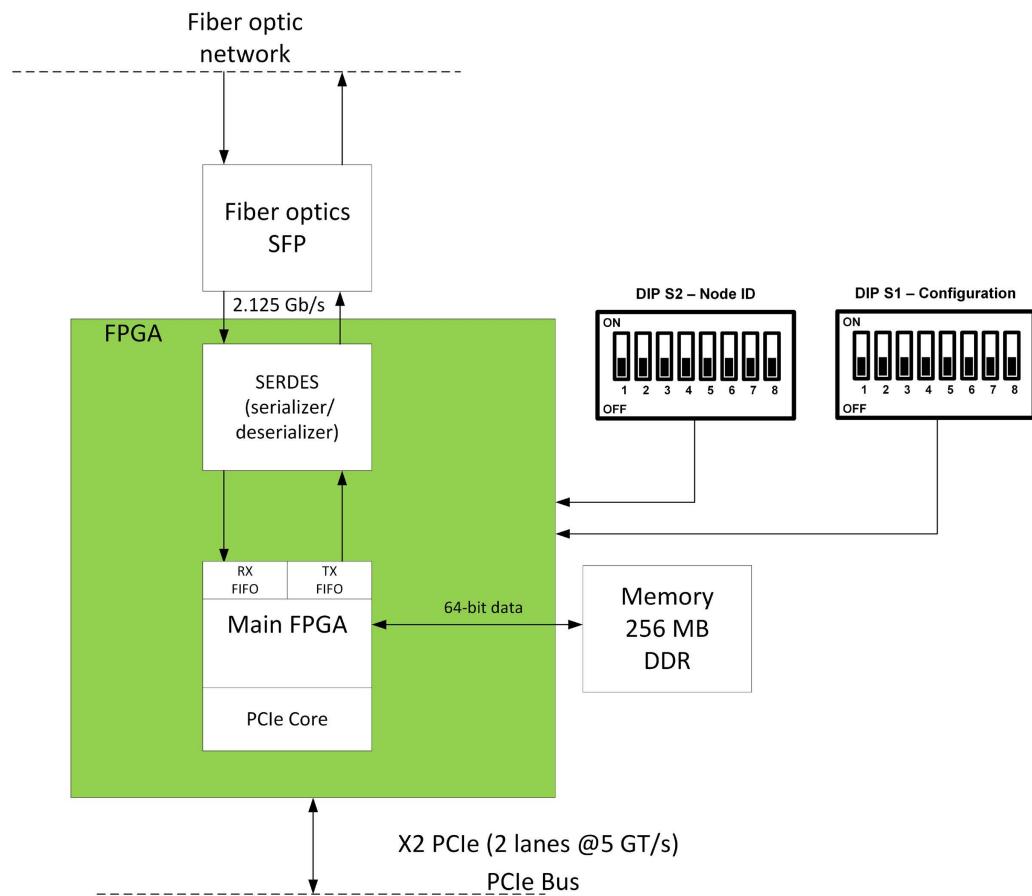

## 2 Über ibaFOB-R

Die *ibaFOB-R*-Karte ist eine PCI Express (PCIe)-Karte aus der Familie der iba-Lichtwellenleiterkarten. Die Karte passt sowohl in Low Profile- als auch Standard-PCIe-Steckplätze.

Die *ibaFOB-R*-Karte ist netzwerkkompatibel mit anderen Reflective Memory-Produkten, die mit 2,125 GBaud arbeiten.

Zwei oder mehr *ibaFOB-R*-Karten können zusammen mit anderen Reflective Memory-Produkten über Standard-LWL-Kabel in ein Netzwerk integriert werden. Jede Karte im Netzwerk wird als „Knoten“ bezeichnet.

Mit Reflective Memory können Rechner, Workstations, SPS und andere eingebettete Steuerungen mit unterschiedlichen Architekturen und verschiedenen Betriebssystemen Daten in Echtzeit austauschen. *ibaFOB-R* ist schnell, flexibel und einfach zu bedienen.

Die Daten werden durch Schreiben in den lokalen RAM-Speicher übertragen, und global an alle Karten im Netzwerk weitergegeben.

Die integrierte Schaltung überträgt die Daten automatisch an alle anderen Knoten, ohne dass ein Host-Prozessor beteiligt ist. Ein Blockdiagramm der *ibaFOB-R*-Karte ist in nachfolgender Abbildung dargestellt.

## 2.1 Eigenschaften

Die *ibaFOB-R*-Karte hat folgende Eigenschaften:

- Einfach zu bedienendes Hochgeschwindigkeits-LWL-Netzwerk (2,125 GBaud seriell)

- PCI Express-Schnittstelle (bis zu 2 aktive Lanes über einen 4x-Anschluss, Geschwindigkeit bis zu Gen2)

- Kein Host-Prozessor für den Betrieb des Netzwerks erforderlich

- Bis zu 256 Knoten

- Bis zu 500 m mit 50/125 µm Multimode-Faser, 300 m mit 62,5/125 µm Multimode-Faser

- Dynamische Paketgröße, 4 bis 64 Bytes Nutzdaten pro Paket

- Übertragungsrate im LWL-Netz 40 MB/s bis 162 MB/s

- 256 MB Reflective Memory

- Unabhängiger DMA-Kanal (Direct Memory Access)

- Vier allgemeine Netzwerk-Interrupts; mit jeweils 32 Bit Daten

- Wählbare PCI PIO Fenstergröße (2 MB, 16 MB, 64 MB, 256 MB)

- RoHS-konform

## 2.2 PCI Express-Konformität

Die *ibaFOB-R*-Karte kann mit jedem geeigneten PCIe-kompatiblen Motherboard mit einem PCIe 4x-Steckplatz (oder höher) betrieben werden. Die *ibaFOB-R*-Karte erfüllt die Anforderungen der PCI-Express-Spezifikation, Revision 2.1.

## 2.3 Hersteller- und Gerätekennung

Das PCI Configuration-Register, das für die Vendor ID (Hersteller-ID) reserviert ist, hat den Wert 0x167F für iba AG.

Das PCI Configuration-Register, das für die Geräte-ID reserviert ist, hat den Wert 0x5565. Der Wert gibt den Kartentyp der iba AG für diese Karte an sowie den Typ der Reflective Memory-Familie.

## 3 Sicherheitshinweise

Beachten Sie die folgenden Sicherheitshinweise für *ibaFOB-R*.

### 3.1 Bestimmungsgemäßer Gebrauch

Die Karte ist ein elektrisches Betriebsmittel. Diese darf nur für folgende Anwendungen verwendet werden:

- Automatisierung von Industrieanlagen

- Messdatenerfassung und Messdaten-Analyse

- Anwendungen von iba-Software-Produkten (*ibaPDA*)

Der Einsatz der *ibaFOB-R*-Karte in Fremdsystemen ist nur nach Rücksprache mit der iba AG möglich.

### 3.2 Spezielle Sicherheitshinweise

---

#### Gefahr durch Stromschlag!

Trennen Sie vor dem Öffnen des Gerätes die Stromversorgung vom Rechner, um einen elektrischen Schlag zu vermeiden!

Bauen Sie die Karte nicht ein oder aus, während die Stromversorgung eingeschaltet ist.

---

#### Vorsicht!

Elektrostatische Entladungen können die Karte beschädigen! Um elektrostatische ESD-Schäden zu vermeiden, entladen Sie Ihren Körper elektrisch, bevor Sie die Karte berühren.

Sie können Ihren Körper entladen, indem Sie unmittelbar vor der Arbeit mit der Karte einen leitfähigen, geerdeten Gegenstand berühren (z. B. metallische Gehäuseteile, Steckdosen-Schutzleiterkontakt).

---

## 4 Lieferumfang

Überprüfen Sie nach dem Auspacken die Vollständigkeit und die Unversehrtheit der Lieferung.

Im Lieferumfang sind enthalten:

- *ibaFOB-R*-Karte mit Standard-Slotblende

- Montiertes Multimode-SFP-Modul

- Low Profile-Slotblende, für den Austausch der Standard-Slotblende, wenn die Karte in einen Low Profile-PCIe-Steckplatz eingebaut werden soll.

Weiteres, nicht im Lieferumfang enthaltenes Zubehör (wie z.B. LWL-Kabel), finden Sie unter

[www.iba-ag.com](http://www.iba-ag.com).

## 5 Systemvoraussetzungen

Beachten Sie die folgenden Voraussetzungen für den Einsatz der *ibaFOB-R*-Karte.

### Hardware

Windows-PC mit folgender Mindestausstattung:

- Pentium IV/3 GHz

- Mindestens ein freier PCIe 2.0-x4-kompatibler Steckplatz

- 4 GByte RAM

- Freier Speicherplatz > 10 GByte

Weitere Informationen zu den iba-Industrierechnern finden Sie unter [www.iba-ag.com](http://www.iba-ag.com).

### Software

- *ibaPDA* Version 8.8 oder höher

## 6 Karte ein- und ausbauen

Beachten Sie die folgenden Warnhinweise bei allen Arbeiten mit den Karten.

---

### Gefahr durch Stromschlag!

Trennen Sie vor dem Öffnen des Gerätes die Stromversorgung vom Rechner, um einen elektrischen Schlag zu vermeiden!

Bauen Sie die Karte nicht ein oder aus, während die Stromversorgung eingeschaltet ist.

---

### Vorsicht!

Elektrostatische Entladungen können die Karte beschädigen! Um elektrostatische ESD-Schäden zu vermeiden, entladen Sie Ihren Körper elektrisch, bevor Sie die Karte berühren.

Sie können Ihren Körper entladen, indem Sie unmittelbar vor der Arbeit mit der Karte einen leitfähigen, geerdeten Gegenstand berühren (z. B. metallische Gehäuseteile, Steckdosen-Schutzleiterkontakt).

---

### 6.1 Karte einbauen

1. Fahren Sie den Rechner herunter.

2. Ziehen Sie den Netzstecker und öffnen Sie den Rechner, um an die PCIe-Steckplätze zu gelangen.

3. Nehmen Sie die Karte vorsichtig aus der Verpackung. Verwenden Sie ein Erdungskabel oder leiten Sie eventuelle elektrostatische Aufladungen ab, bevor Sie die Karte berühren.

4. Fassen Sie die Karte an der vorderen Blende und an der hinteren oberen Ecke an. Berühren Sie nicht die Kontakte. Positionieren Sie die Schalter S1 und S2, Beschreibung siehe Kapitel **↗ Konfiguration**, Seite 18.

5. Die *ibaFOB-R*-Karte ist im Low Profile-Formfaktor ausgeführt.

Die Karte wird mit einer Slotblende in Standardhöhe ausgeliefert. Eine Low Profile-Slotblende ist im Lieferumfang enthalten. Wenn Sie für Ihren Rechner eine Low Profile-Karte benötigen, ersetzen Sie die Standard-Slotblende der Karte durch die mitgelieferte Low Profile-Slotblende.

6. Stecken Sie die Karte vorsichtig in einen freien PCIe-Steckplatz und befestigen Sie die Karte am Gehäuse des Rechners.

7. Schließen Sie den Rechner.

8. Stecken Sie den Netzstecker in die Schutzkontakt-Steckdose und starten Sie den Rechner.

## 6.2 Karte ausbauen

1. Fahren Sie den Rechner herunter.

2. Ziehen Sie den Netzstecker und öffnen Sie den PC, um an die PCIe-Steckplätze zu gelangen.

3. Lösen Sie alle äußereren Verbindungsleitungen von der Karte.

4. Lösen Sie die Befestigungsschrauben.

5. Ziehen Sie die Karte vorsichtig aus dem PCI(e)-Steckplatz heraus. Bewahren Sie die Karte in einer geeigneten Verpackung auf.

## 7 Beschreibung

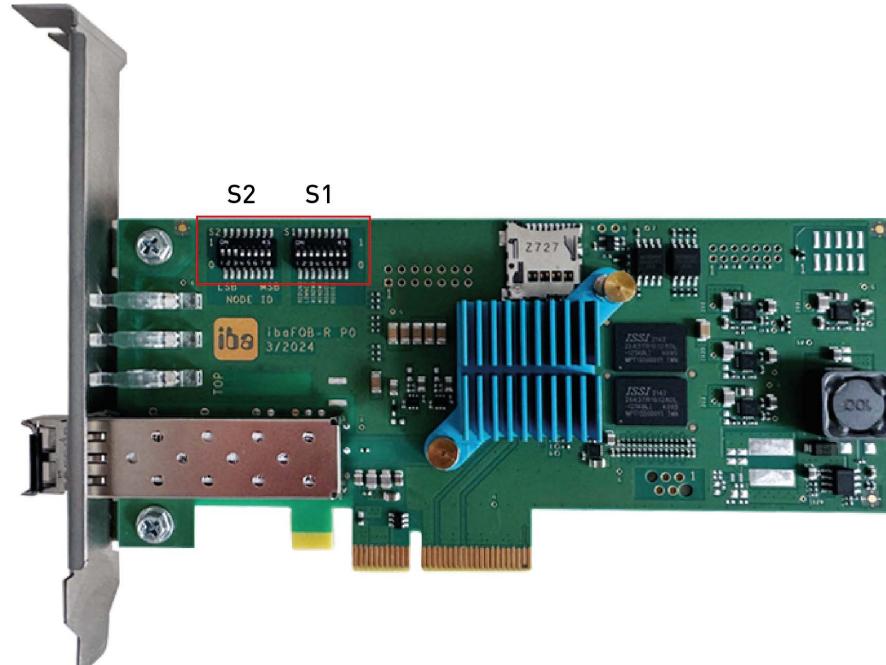

Hier finden Sie Ansichten und Beschreibungen zur Karte *ibaFOB-R*.

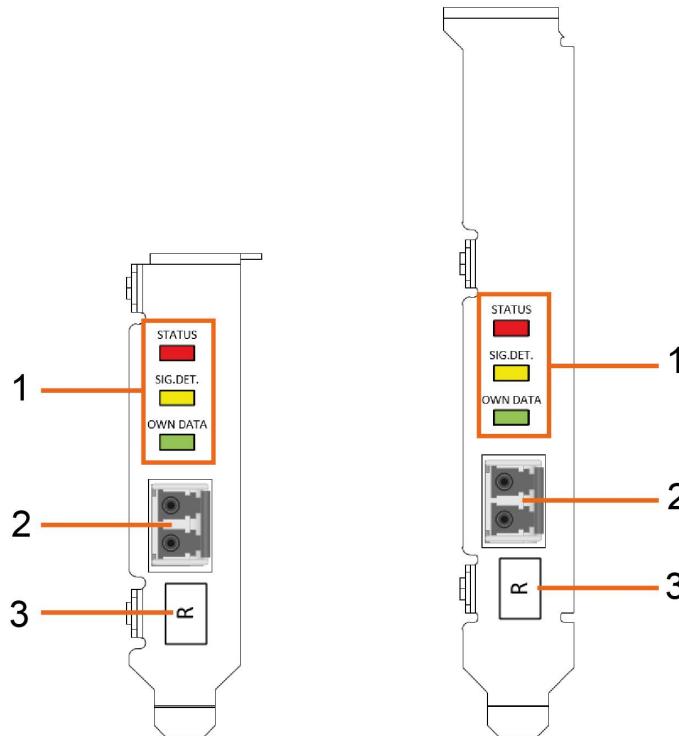

### 7.1 Vorderansicht

Links: *ibaFOB-R*-Karte mit Low Profile-Slotblende, rechts: *ibaFOB-R*-Karte mit Standard-Slotblende

- 1 Betriebszustandsanzeigen

- 2 Lichtwellenleiter-Anschluss (SFP)

- 3 Kennung für Karten der ibaFOB-Familie

Die Kennung (3) dient zur besseren Unterscheidung der einzelnen *ibaFOB*-Kartentypen. Folgende Kennung steht für folgende Kartentypen:

- |            |                              |

|------------|------------------------------|

| <b>D</b>   | ibaFOB-D und ibaFOB-Dexp     |

| <b>TDC</b> | ibaFOB-TDC und ibaFOB-TDCexp |

| <b>SD</b>  | ibaFOB-SD und ibaFOB-SDexp   |

| <b>PC</b>  | ibaFOB-PlusControl           |

| <b>R</b>   | ibaFOB-R                     |

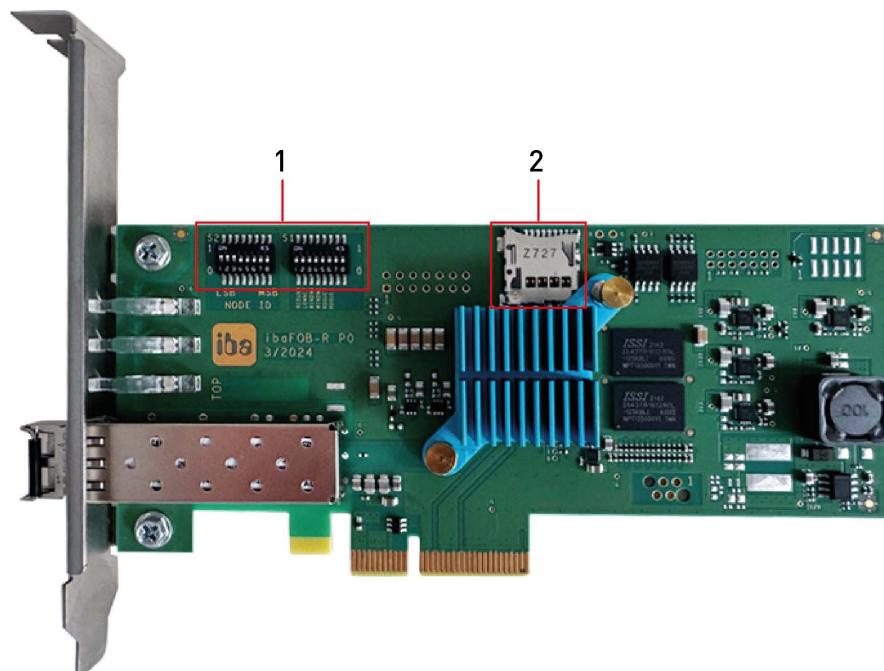

## 7.2 Draufsicht

- 1 DIP-Schalter, siehe auch Kapitel **Konfiguration**, Seite 18

2 SD-Steckplatz, nur für Service-Zwecke

## 7.3 Anzeigeelemente

Der Betriebszustand des Gerätes wird durch farbige Status-LEDs angezeigt.

| <b>LED</b>    | <b>Farbe</b> | <b>Beschreibung</b>                                                                                                                                      |

|---------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status        | Rot/aus      | Benutzerdefinierte Statusanzeige. Wird vom Host gesteuert.<br>Kann in ibaPDA im I/O-Manager auf blinkend gesetzt werden.                                 |

|               | Blau         | Das Hostsystem hat die Karte am PCIe-Bus deaktiviert.<br>(Die Karte befindet sich im PCI-Power-Management-Status D3 oder wird im Zustand Reset gehalten) |

| Signal Detect | Gelb         | Gültiges optisches Signal auf der LWL-Verbindung erkannt                                                                                                 |

|               | Blau         | Ungültiges optisches Signal auf der LWL-Verbindung erkannt                                                                                               |

|               | aus          | Kein optisches Signal auf der LWL-Verbindung erkannt                                                                                                     |

| Own Data      | Grün         | Zeigt an, wann eigene gesendete Pakete wieder empfangen werden.                                                                                          |

Der Standardzustand der Status-LED beim Einschalten ist "an".

Die LED Status ist eine benutzerdefinierte Anzeige auf der Karte und kann durch Beschreiben von Bit 31 des Control and Status-Registers ein- oder ausgeschaltet werden.

Die LED *Signal Detect* leuchtet, wenn der Empfänger Licht erkennt. Damit lässt sich einfach überprüfen, ob das optische Netzwerk ordnungsgemäß mit dem Empfänger verbunden ist.

Die LED *Own Data* leuchtet, wenn die Karte ihre eigenen Daten erkannt hat, die über das Netzwerk zurückkommen. Die LED kann ausgeschaltet werden, indem Bit 0 des Control and Status-Registers gelöscht wird.

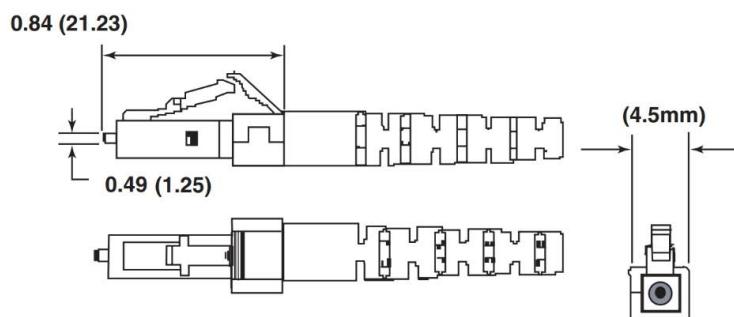

## 7.4 LWL-Verbindungen

In die Small Form-Factor Pluggable (SFP) LWL-Schnittstelle der *ibaFOB-R*-Karte kann ein Singlemode-SFP- oder Multimode-SFP-Modul eingebaut werden.

Die folgende Tabelle gibt einen Überblick über die Kabelspezifikationen für Singlemode- und Multimode-Fasern.

| Eigenschaft                  | Singlemode                          | Multimode                           |

|------------------------------|-------------------------------------|-------------------------------------|

| Durchmesser Faserkern        | $8,3 \pm 1,0 \mu\text{m}$           | $50/62,5 \pm 3 \mu\text{m}$         |

| Durchmesser Glasmantel       | $125 \pm 2 \mu\text{m}$             | $125 \pm 2 \mu\text{m}$             |

| Außendurchmesser des Mantels | $3,0 \text{ mm} \pm 0,1 \text{ mm}$ | $3,0 \text{ mm} \pm 0,1 \text{ mm}$ |

| Dämpfung                     | 0,8 dB/km (max) bei 1310 nm         | 4,0 dB/km (max) bei 850 nm          |

| Bandbreite                   | N/A                                 | 160 bis 300 MHz*km (min) bei 850 nm |

| UL                           | Typ OFNR, CSA Typ OFN FT4           | Typ OFNR, CSA Typ OFN FT4           |

Die *ibaFOB-R*-Karte wird mit einem installierten Multimode-SFP-Modul mit LC-LWL-Anschlüssen ausgeliefert.

LC LWL-Stecker:

Dimensions: inches (mm)

## 8 Konfiguration

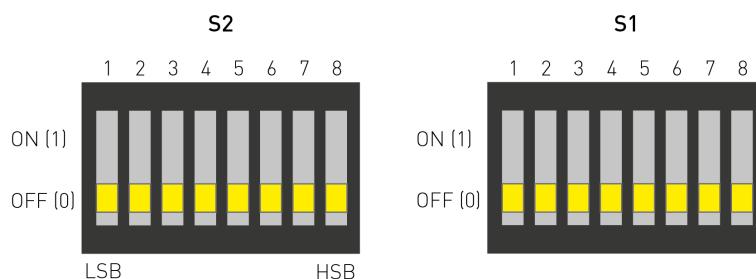

Vor dem Einbau der Karte müssen Einstellungen mit den beiden DIP-Schaltern S1 und S2 auf der *ibaFOB-R*-Karte vorgenommen werden.

Die nachfolgende Abbildung zeigt die Anordnung der Schalter S1 und S2.

Werkseinstellung der DIP-Schalter:

### 8.1 Konfiguration Schalter S1

Vor dem Einbau der *ibaFOB-R*-Karte in das Host-System muss der Schalter S1 für die entsprechende Betriebsart konfiguriert werden. Der Schalter S1 steuert sechs Funktionen auf der Karte.

**Die Einstellungen am Schalter S1 dürfen nur im ausgeschalteten Zustand durchgeführt werden.**

---

#### Tipp

In den meisten Fällen ist es nicht notwendig, den Schalter S1 zu konfigurieren. Die Werkseinstellung der Schalter kann beibehalten werden, d. h. alle Schalter stehen auf OFF.

- S1 Position 1: Auswahl des Netzübertragungsmodus: redundant (ON) oder nicht-redundant (OFF).

- S1 Position 2: die Übertragungsgeschwindigkeit der Karte im Netzwerk wird reduziert, um eine Überlastung der anderen Netzteilnehmer zu vermeiden (ON). Steht der Schalter auf OFF ist die volle Übertragungsbandbreite verfügbar.

- S1 Position 3 und 4: Auswahl der PCI-Fenstergröße für PIO-Speicherzugriffe. In der Default-Einstellung (beide Schalter 3 und 4 auf OFF) wird die gesamte installierte Speichergröße verwendet. Die Größe des reduzierten Speicherfensters kann zwischen 64 MB, 16 MB und 2 MB gewählt werden.

- S1 Position 5: die Funktion Rogue Master 0 wird aktiviert (Position ON) oder deaktiviert.

- S1 Position 6: die Funktion Rogue Master 1 wird aktiviert (Position ON) oder deaktiviert.

- S1 Position 7: derzeit reserviert (sollte in der OFF-Position belassen werden).

- S1 Position 8: derzeit reserviert (sollte in der OFF-Position belassen werden).

Die folgenden Tabellen geben einen Überblick über die S1-Einstellungen.

#### Konfigurationseinstellungen Schalter S1

|                                              |                                                                 |                                             |                                                                            |

|----------------------------------------------|-----------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------|

| Position 1                                   | OFF: Kein-Redundanzmodus<br>ON: Redundanzmodus                  | Position 2                                  | OFF: volle Übertragungsbandbreite<br>ON: reduzierte Übertragungsbandbreite |

| Position 5                                   | OFF: Rogue Master 0 deaktiviert<br>ON: Rogue Master 0 aktiviert | Position 6                                  | OFF: Rogue Master 1 deaktiviert<br>ON: Rogue Master 1 aktiviert            |

| Position 3 und 4: siehe nachfolgende Tabelle |                                                                 | <b>Werkseinstellung:</b> Positionen 1-8 OFF |                                                                            |

#### Schalter S1 PCI Fensterkonfiguration

| PCI Fenstergröße          | S1 Position 3 | S1 Position 4 |

|---------------------------|---------------|---------------|

| 256 MB (Werkseinstellung) | OFF           | OFF           |

| 64 MB                     | ON            | OFF           |

| 16 MB                     | OFF           | ON            |

| 2 MB                      | ON            | ON            |

## 8.2 Konfiguration Schalter S2

Vor dem Einbau der *ibaFOB-R*-Karte in ein Host-System muss die gewünschte Knoten-ID (Node ID) mit dem Schalter S2 eingestellt werden. Jeder Knoten im Netz muss eine eindeutige Knoten-ID haben.

Der Schalter S2 steht für die 8 Bits der Knoten-ID. Mit den 8 ID-Bits können Knoten-IDs von 0x00 bis 0xFF (255 dezimal) eingestellt werden.

Schalter 2, Position 1 (links) entspricht dem niedrigstwertigen Bit der Knoten-ID und Schalter 2, Position 8 (rechts) entspricht dem höchstwertigen Bit der Knoten-ID.

Befindet sich der Schalter S2 in der OFF-Position, wird das Knoten-ID-Bit auf *low* (0) gesetzt, befindet sich der Schalter S2 in der ON-Position, wird das binäre Knoten-ID-Bit auf *high* (1) gesetzt.

Die folgende Tabelle enthält Beispiele für mögliche Knoten-IDs.

| S2<br>Pos. 1                                | S2<br>Pos. 2 | S2<br>Pos. 3 | S2<br>Pos. 4 | S2<br>Pos. 5 | S2<br>Pos. 6 | S2<br>Pos. 7 | S2<br>Pos. 8 | Knoten-ID<br>Hex (Dec.) |

|---------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------------------|

| ON                                          | ON           | ON           | ON           | ON           | ON           | ON           | ON           | 0xFF (255)              |

| OFF                                         | OFF          | OFF          | OFF          | OFF          | OFF          | OFF          | ON           | 0x80 (128)              |

| OFF                                         | OFF          | OFF          | OFF          | OFF          | OFF          | ON           | OFF          | 0x40 (64)               |

| OFF                                         | OFF          | OFF          | OFF          | OFF          | ON           | OFF          | OFF          | 0x20 (32)               |

| OFF                                         | OFF          | OFF          | OFF          | ON           | OFF          | OFF          | OFF          | 0x10 (16)               |

| OFF                                         | OFF          | OFF          | ON           | OFF          | OFF          | OFF          | OFF          | 0x8 (8)                 |

| OFF                                         | OFF          | ON           | OFF          | OFF          | OFF          | OFF          | OFF          | 0x4 (4)                 |

| OFF                                         | ON           | OFF          | OFF          | OFF          | OFF          | OFF          | OFF          | 0x2 (2)                 |

| ON                                          | OFF          | 0x1 (1)                 |

| OFF                                         | OFF          | OFF          | OFF          | OFF          | OFF          | OFF          | OFF          | 0x0 (0)                 |

| <b>Werkseinstellung:</b> Positionen 1-8 OFF |              |              |              |              |              |              |              |                         |

### 8.2.1 Wichtige Hinweise vor der Installation

Beachten Sie bei der Konfiguration der Schalter S1 und S2 folgende Hinweise:

#### Hinweis

Jedes Reflective Memory-Modul im Reflective Memory-Netzwerk muss eine eindeutige Knoten-ID haben, um sich selbst zu identifizieren. Bevor Sie die Knoten-ID mit dem Schalter S2 einstellen, überprüfen Sie die Knoten-ID aller anderen Teilnehmer im Netz. Es gibt keine interne Erkennung von doppelten Knoten in einem Netzwerk!

#### Hinweis

Alle Knoten im Ring müssen für den gleichen Übertragungsmodus konfiguriert sein, entweder für den redundanten oder den nicht redundanten Übertragungsmodus. Eine falsche Einstellung führt dazu, dass einzelne Pakete aus dem Ring entfernt werden und die Daten verloren gehen.

#### Hinweis

Im Ring darf nicht mehr als ein Knoten mit aktiviertem Rogue Master 0 konfiguriert werden. Wenn zwei oder mehr Knoten mit aktiviertem Rogue Master 0 konfiguriert sind, werden einzelne Pakete aus dem Ring entfernt, und diese Daten gehen verloren.

---

**Hinweis**

Im Ring darf nicht mehr als ein Knoten mit aktiviertem Rogue Master 1 konfiguriert werden. Wenn zwei oder mehr Knoten mit aktiviertem Rogue Master 1 konfiguriert sind, werden einzelne Pakete aus dem Ring entfernt, und diese Daten gehen verloren.

---

## 9 Konfiguration in ibaPDA

Diese Dokumentation beschreibt alle Funktionen der *ibaFOB-R*-Karte beim Einsatz im *ibaPDA*-System, einschließlich zusätzlicher Informationen zu Diagnose- und Fehlerbehebung.

---

### Andere Dokumentation

Informationen zur Konfiguration in *ibaPDA* finden Sie im Handbuch

*ibaPDA-Interface-Reflective-Memory*.

---

Für die Datenerfassung über Reflective Memory mit *ibaPDA* ist die Schnittstellenlizenz *ibaPDA-Interface-Reflective-Memory* (31.001220) Voraussetzung und muss separat erworben werden (wie bisher bei ABACO und früheren Reflective Memory-Karten).

# 10 Systemintegration

---

## Hinweis

Dieses Kapitel richtet sich an Systemintegratoren, die die *ibaFOB-R*-Karte in ihrem Automatisierungs- oder Embedded-System einsetzen wollen.

Für Anwender, die die *ibaFOB-R*-Karte zusammen mit *ibaPDA* einsetzen, sind diese Detailinformationen weniger relevant.

---

Die folgenden Abschnitte beschreiben die Funktionalität der *ibaFOB-R*-Karte. Außerdem werden die wichtigsten Schaltungen und ihre Funktionen beschrieben.

In diesem Abschnitt werden auch die Control and Status-Register beschrieben, die für den Betrieb relevant sind. Eine ausführliche Beschreibung dieser Control and Status-Register finden Sie in Kapitel **Anforderungen an die Programmierung**, Seite 28.

## 10.1 Grundlegende Funktionen und Bedienung

Die einzelnen Knoten des Reflective Memory-Netzwerks sind über LWL in einer Reihenschaltung (daisy chain) miteinander verbunden. Der Sender der ersten Karte muss mit dem Empfänger der zweiten Karte verbunden werden. Der Sender der zweiten Karte ist mit dem Empfänger der dritten Karte verbunden, und so weiter, bis der Ring wieder am Empfänger der ersten Karte geschlossen wird.

Alternativ kann jeder Knoten über einen oder mehrere Reflective Memory Hubs an das Ringnetz angeschlossen werden.

Es ist wichtig, dass das Ringnetzwerk geschlossen ist (d. h. jeder Empfänger und jeder Sender muss angeschlossen sein). Jeder Knoten muss eine eindeutige Knoten-ID haben, die mit dem Schalter S2 eingestellt wird (d. h. zwei Knoten dürfen nicht die gleiche Knoten-ID haben). Die Reihenfolge der Knoten-IDs ist unerheblich.

Eine Datenübertragung über das Netzwerk wird durch einen Schreibvorgang vom Hostsystem in den Onboard-RAM-Speicher initiiert. Das Schreiben kann ein einfacher PIO-Schreibvorgang sein oder aufgrund eines DMA-Zyklus durch die residente DMA-Engine erfolgen.

Während des Schreibvorgangs in den Arbeitsspeicher schreibt die Schaltung auf der *ibaFOB-R*-Karte die Daten und andere relevante Informationen automatisch in den Sende-FIFO.

Die Sendeschaltung holt die Daten aus dem Sende-FIFO und packt sie in ein Paket variabler Länge von 4 bis 64 Byte, das über die LWL-Schnittstelle zum Empfänger der nächsten Karte übertragen wird. Der Empfänger prüft dann das Paket auf Fehler. Wenn die fehlerfreien Daten empfangen wurden, speichert die Empfangsschaltung die Daten im Empfangs-FIFO der Karte. Aus dem Empfangs-FIFO schreibt eine andere Schaltung die Daten in das lokale Onboard-RAM an der gleichen relativen Speicherposition wie der Ursprungsknoten.

Diese Schaltung leitet die Daten auch gleichzeitig in den karteneigenen Sende-FIFO. Von dort aus wird der Prozess wiederholt, bis die Daten zum Empfänger des Ursprungsknotens zurückkehren. Am Ursprungsknoten wird das Datenpaket aus dem Netz entfernt.

## 10.2 ibaFOB-R Hardware-Register

Anwender, die mehr als die Standard-Lese- und Schreiboperationen durchführen wollen, müssen die Bits innerhalb der drei Registersätze verstehen und entsprechend ändern. Die drei Registersätze sind:

- PCI Configuration Register, siehe [PCI Configuration Register](#), Seite 28

- Local Configuration Register, siehe [Local Configuration Register](#), Seite 37

- RFM Control and Status Register, siehe [RFM Control and Status Register](#), Seite 41

### PCI Configuration Register

Dieser Registersatz ist durch die PCI Local Bus Specification vordefiniert und ist Standard für alle PCI- und PCI Express-Geräte. Dieser Registersatz enthält die Vendor ID, Device ID, Subsystem Vendor ID und Base Address-Register. Die PCI Configuration-Register werden zunächst initialisiert und dann je nach Bedarf vom PCI-Bus-System-BIOS geändert. Der Registersatz wird vom Benutzer nur selten geändert, aber um die anderen beiden Registersätze zu lokalisieren, ist es notwendig, diese Register, insbesondere die Base Address-Register, lesen zu können.

### Local Configuration Register

Base Address Register 0 enthält die Anfangsadresse für die Local Configuration Register. Zu den Local Configuration-Registern, die für den Betrieb von *ibaFOB-R* relevant sind, gehören das Interrupt Control and Status-Register (INTCSR) und die DMA Control-Register.

### RFM Control and Status Register

Die RFM Control and Status-Register realisieren die speziellen Funktionen der *ibaFOB-R*-Reflective Memory-Karte. Diese Funktionen umfassen den RFM-Betriebsstatus, die detaillierte Steuerung der RFM-Quellen für den PCI-Interrupt und den Netzwerk-Interrupt-Zugriff. Der Zugriff auf diese Register erfolgt mit einem Offset von der im Base Address Register 2 enthaltenen Adresse.

## 10.3 Reflective Memory RAM auf ibaFOB-R

Die *ibaFOB-R*-Karte ist mit 256 MB Onboard-Reflective Memory RAM ausgestattet.

Das RAM beginnt an der im Base Address-Register 3 angegebenen Position.

Der Offset-Adressbereich ist 0 bis 0xFFFFFFFF für 256 MB.

Dieser Adressbereich kann durch entsprechende Einstellung des Schalters S1 eingeschränkt werden, siehe Kapitel [Konfiguration Schalter S1](#), Seite 18.

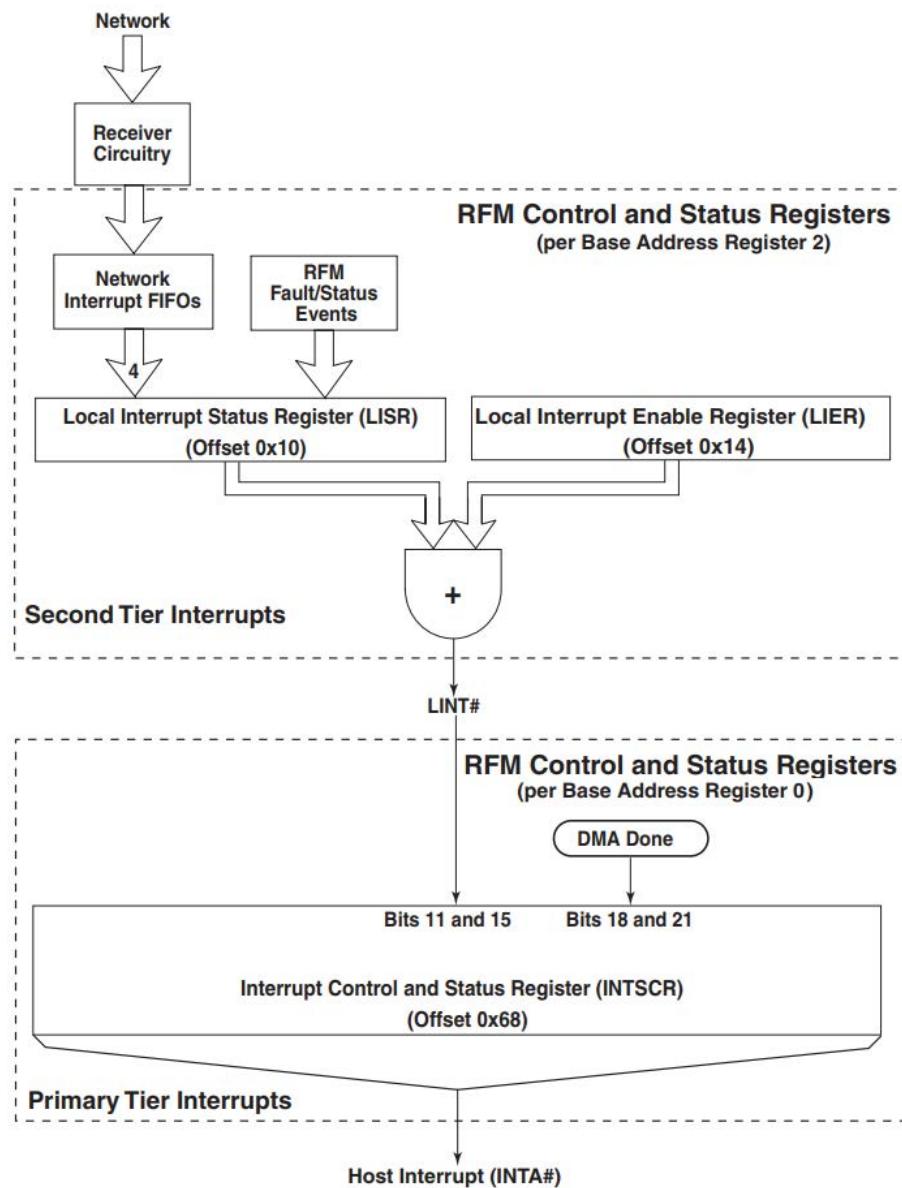

## 10.4 Interrupt generieren

Die *ibaFOB-R*-Karte verfügt über einen einzigen Interrupt-Ausgang am PCIe-Bus.

Der Interrupt kann als Legacy-INTA#-Interrupt auf Nachrichtenebene oder als MSI- oder MSI-X-Ereignisinterrupt ausgelöst werden, wenn dies von der Systemsoftware aktiviert wird.

Ein oder mehrere Ereignisse auf der *ibaFOB-R*-Karte können den Interrupt auslösen. Die Quellen des Interrupts können durch mehrere Register individuell aktiviert und überwacht werden. Die Interrupt-Schaltung der *ibaFOB-R*-Karte ist in zwei Ebenen gegliedert.

Die erste Ebene der Interrupts wird durch das INTCSR im Local Configuration-Register mit dem Offset 0x68 aktiviert und überwacht. Die Quellen für die Interrupts der ersten Ebene sind:

1. DMA Done

2. Local Interrupt Input

Die erste Ebene der Interrupt-Quelle (1) kann verwendet werden, um das Ende einer DMA-Übertragung zu melden, und muss in den DMA-Registern konfiguriert werden. Die andere Interrupt-Quelle der ersten Ebene Stufe (2) ist der lokale Interrupt-Eingang.

Alle Interrupts der zweiten Ebene werden über den lokalen Interrupt-Eingang geleitet. Zu den Interrupts der zweiten Ebene gehören mehrere Betriebsstatusbits, Fehler und Netzwerkinterrupts. Die Interrupts der zweiten Ebene werden über die beiden RFM Control and Status-Register, das Local Interrupt Status Register (LISR) und das Local Interrupt Enable Register (LIER), ausgewählt und überwacht.

Eine detaillierte Beschreibung dieser beiden Register finden Sie im Kapitel **↗ RFM Control and Status Register**, Seite 41.

Ein Blockdiagramm der Interrupt-Schaltung finden Sie in nachfolgender Abbildung.

## 10.5 Netzwerk Interrupts

Die *ibaFOB-R*-Karte kann sowohl Interrupt-Pakete als auch Datenpakete über das Netzwerk weiterleiten. Die Netzwerk-Interrupt-Pakete können an einen bestimmten Knoten gesendet werden oder global an alle anderen Knoten im Netzwerk. Jedes Netzwerk-Interrupt-Paket enthält die Knoten-ID des Absenders, die Knoten-ID des Ziels, den Interrupt-Typ und 32 Bit benutzerdefinierte Daten.

Zu den Arten von Netzwerk-Interrupts gehören vier allgemeine Interrupts und ein Reset-Node-Request-Interrupt. Knotenspezifische Interrupts werden gesendet, indem drei RFM Control and Status-Register konfiguriert werden. Jeder Empfangsknoten wertet die Interrupt-Pakete beim Passieren aus. Wenn ein allgemeiner Interrupt an diesen Knoten gerichtet ist, wird die Knoten-ID des Absenders im entsprechenden Sender-ID-FIFO (einem von vier) gespeichert. Jeder Sender-ID-FIFO umfasst mindestens 127 Speicherplätze. Die Begleitdaten werden in einem Begeleitdaten-FIFO gespeichert.

Jeder der Netzwerk-Interrupts kann, wenn er über die Register LISR, LIER und INTCSR aktiviert ist, auch einen Host-PCI-Interrupt an jedem empfangenden Knoten auslösen.

Der Reset Node Request Interrupt wird nicht in einem FIFO gespeichert wie die vier allgemeinen Interrupts. Außerdem erfolgt kein sofortiger Reset der Karte. Stattdessen wird ein Bit im LISR-Register gesetzt, das einen PCI-Interrupt auslöst, wenn dies aktiviert ist. Der tatsächliche Reset der Karte sollte vom Host-System ordnungsgemäß durchgeführt werden. Die Benutzeranwendung könnte diesen Netzwerk-Interrupt jedoch für beliebige Aufgaben verwenden.

## 10.6 Redundanter Übertragungsmodus

Die *ibaFOB-R*-Karte ist für den Betrieb im redundanten Übertragungsmodus geeignet. Ist der Schalter S1, Position 1 in der Stellung ON, ist die Karte für den redundanten Betrieb konfiguriert. Im redundanten Übertragungsmodus wird jedes erzeugte Paket zweimal übertragen, unabhängig von der Paketgröße. Die Empfangsschaltung jedes Knotens im Netz wertet jede der redundanten Übertragungen aus. Wenn bei der ersten Übertragung keine Fehler festgestellt werden, wird sie zur Aktualisierung des Onboard-Speichers verwendet und die zweite Übertragung wird verworfen. Wenn die erste Übertragung jedoch einen Fehler enthält, wird die zweite Übertragung zur Aktualisierung des Onboard-Speichers verwendet, vorausgesetzt, sie weist keine Übertragungsfehler auf. Wenn bei beiden Übertragungen Fehler festgestellt werden, werden die Übertragungen nicht ausgeführt und die Daten werden vollständig aus dem Netz entfernt.

Der redundante Übertragungsmodus verringert die Wahrscheinlichkeit, dass Daten im Netz verloren gehen. Der redundante Übertragungsmodus verringert jedoch auch die Datenübertragungsrate im Netz. Die Übertragungsgeschwindigkeit für ein einzelnes DWord (Doppelwort = 4 Byte) sinkt von der nicht-redundanten Geschwindigkeit von 43 MB/s auf etwa 20 MB/s. Die Übertragungsgeschwindigkeit für 16 DWords (64 Byte) sinkt von der nicht-redundanten Geschwindigkeit von 170 MB/s auf die redundante Geschwindigkeit von 85 MB/s.

## 10.7 Rogue Packet Removal Betriebsmodus

Ein Rogue-Paket ist ein Paket, das zu keinem Knoten im Netz gehört. Die grundlegende Funktionsweise von Reflective Memory besteht darin, dass ein Knoten als Antwort auf einen Speicherzugriff des Hosts ein Paket über das Netz sendet. Das Paket wird im gesamten Netz an alle Knoten übertragen, bis es zum Ursprungsknoten zurückkehrt. Der Ursprungsknoten muss das Paket aus dem Netz entfernen. Wenn das Paket jedoch auf dem Weg durch einen anderen Knoten fälschlicherweise verändert wird oder wenn der Ursprungsknoten nicht mehr richtig funktioniert, erkennt der Ursprungsknoten das Paket möglicherweise nicht als sein eigenes und entfernt es nicht aus dem Netz. In diesem Fall durchläuft das Paket weiterhin das Netz als „Rogue-Paket“.

Rogue-Pakete sind sehr selten. Beim Ein- und Ausschalten eines Knotens, der mit einem optischen Hub verbunden ist, könnte ein Rogue-Paket erzeugt werden. Dies kann auch beim Anschließen oder Trennen von LWL-Kabeln passieren. Ein Rogue-Paket kann entstehen, wenn ein beliebiger Knoten im Netz einen Netz-FIFO überlastet. Ihr Auftreten könnte auf eine Fehlfunktion der Karte hinweisen, die auf ein echtes Bauteilversagen oder auf den Betrieb in einer übermäßig rauen Umgebung zurückzuführen ist. Normalerweise besteht die Lösung darin, die defekte Karte zu isolieren und auszutauschen und/oder die Umgebung zu verbessern. Einige Anwender ziehen es jedoch vor, sporadisch auftretende fehlerhafte Pakete zu tolerieren, anstatt

das System für Wartungsarbeiten anzuhalten, solange die fehlerhaften Pakete aus dem Netz entfernt werden.

Um Toleranz gegenüber Rogue-Paket-Fehlern zu ermöglichen, enthält die *ibaFOB-R*-Karte Schaltungen, mit denen sie als einer von zwei Rogue-Mastern arbeiten kann. Ein Rogue-Master markiert jedes Paket, das von einem anderen Knoten kommt. Wenn dasselbe Paket ein zweites Mal zum Rogue Master zurückkehrt, erkennt der Rogue Master, dass es sich um ein Rogue-Paket handelt und entfernt es aus dem Netzwerk (nachdem das Rogue-Packet jeden Knoten passiert hat). Wenn ein Rogue-Paket erkannt wird, wird im LISR ein Rogue-Paket-Fehler-Flag gesetzt. Die Aktivierung des Rogue-Paket-Fehler-Bits kann optional einen PCI-Interrupt auslösen, um den Host zu informieren, dass die Störung vorliegt. Zwei Rogue Master, Rogue Master 0 und Rogue Master 1, sind zur gegenseitigen Kontrolle vorhanden. Rogue Master 0 wird aktiviert, indem der Schalter S1 in Position 5 auf ON gestellt wird. Rogue Master 1 wird aktiviert, indem der Schalter S1 in Position 6 auf ON gestellt wird. So wie zwei Karten in einem Netzwerk nicht dieselbe Knoten-ID haben sollten, sollten zwei Karten im selben Netzwerk nicht als derselbe Rogue-Master konfiguriert werden. Andernfalls würde einer der beiden fälschlicherweise die vom anderen markierten Pakete entfernen.

## 10.8 Anforderungen an die Programmierung

Grundlegende Schreib- und Leseoperationen der *ibaFOB-R*-Karte erfordern wenig oder keine Software.

Die Karte ist nach dem Einschalten funktionsfähig. Der Benutzer muss auf die PCI Configuration-Register (Base Address-Register 0, 2 und 3) zugreifen können, um zu sehen, wo das System-BIOS die anderen Registersätze und das Reflective Memory gespeichert hat.

Die Lage der Registersätze und des Reflective Memory ist von System zu System unterschiedlich und kann sogar von Steckplatz zu Steckplatz innerhalb eines Systems variieren.

Für Funktionen, die über die Grundeinstellung hinausgehen, wie z. B. das Aktivieren oder Deaktivieren von Interrupts oder die Durchführung von DMA-Zyklen, muss der Benutzer die spezifischen Bit-Zuordnungen der Register innerhalb der drei Registersätze kennen. Diese Informationen werden in diesem Kapitel erläutert.

Die drei Registersätze sind:

- PCI Configuration Register

- Local Configuration Registers

- RFM Control and Status Register

### 10.8.1 PCI Configuration Register

Die PCI Configuration-Register befinden sich in 256 Bytes des PCI Configuration Space, der einer in der PCI-Spezifikation festgelegten Vorlage entspricht.

Obwohl auf die PCI Configuration-Register jederzeit zugegriffen werden kann, werden sie nur selten von der Benutzeranwendung verändert. In den meisten Fällen werden diese von der Systemsoftware konfiguriert.

### PCI Configuration Register

| Adresse (Hex)                                                                                                                 | 31..24                                | 23..16     | 15..8               | 7..0                 |

|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------|---------------------|----------------------|

| 00                                                                                                                            | Geräte-ID                             |            |                     | Vendor ID            |

| 04                                                                                                                            | Status Register                       |            |                     | Command Register     |

| 08                                                                                                                            | Class Code                            |            |                     | Revision ID          |

| 0C                                                                                                                            | BIST*                                 | Header-Typ | Latenz-Timer*       | Cache-Zeilengröße*   |

| 10                                                                                                                            | Base Address Register 0               |            |                     |                      |

| 14                                                                                                                            | Base Address Register 1*              |            |                     |                      |

| 18                                                                                                                            | Base Address Register 2               |            |                     |                      |

| 1C                                                                                                                            | Base Address Register 3               |            |                     |                      |

| 20                                                                                                                            | Base Address Register 4*              |            |                     |                      |

| 24                                                                                                                            | Base Address Register 5*              |            |                     |                      |

| 28                                                                                                                            | Kartenbus CIS Pointer*                |            |                     |                      |

| 2C                                                                                                                            | Subsystem ID                          |            | Subsystem Vendor ID |                      |

| 30                                                                                                                            | Erweiterungs-ROM Base Address*        |            |                     |                      |

| 34                                                                                                                            | Reserviert*                           |            |                     | Capabilities Pointer |

| 38                                                                                                                            | Reserviert*                           |            |                     |                      |

| 3C                                                                                                                            | Max_Lat*                              | Min_Gnt*   | Interrupt Pin       | Interrupt Line       |

| 40..47                                                                                                                        | Power Management Capability Structure |            |                     |                      |

| 48..4F                                                                                                                        | MSI Capability Structure              |            |                     |                      |

| 50..5F                                                                                                                        | Reserviert*                           |            |                     |                      |

| 60..9B                                                                                                                        | PCIe Capability Structure             |            |                     |                      |

| 9C..A7                                                                                                                        | MSI-X Capability Structure            |            |                     |                      |

| A8..FF                                                                                                                        | Reserviert*                           |            |                     |                      |

| Mit * markierte Zellen sind reservierte oder nicht zutreffende Register für <i>ibaFOB-R</i> (Wert nach Reset nicht definiert) |                                       |            |                     |                      |

### PCI Configuration ID Register (Offset 0x00)

| Bit   | Beschreibung                                                | Lesen | Schreiben | Wert nach PCI Reset       |

|-------|-------------------------------------------------------------|-------|-----------|---------------------------|

| 15:0  | <b>Vendor ID</b><br>Identifiziert den Hersteller des Geräts | Ja    | Nein      | 0x167F<br><b>= iba AG</b> |

| 31:16 | <b>Device ID</b><br>Identifiziert das jeweilige Gerät       | Ja    | Nein      | 0x5565                    |

**PCI Command Register (Offset 0x04)**

| Bit | Beschreibung                                                                                                                                                                                                                                                  | Lesen | Schreiben | Wert nach PCI Reset* |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 0   | <b>I/O Space</b><br>Wird eine Eins (1) geschrieben, kann das Gerät auf I/O Space-Zugriffe antworten.<br>Das Schreiben einer Null (0) verhindert, dass das Gerät auf I/O Space-Zugriffe antwortet.                                                             | Ja    | Ja        | 0                    |

| 1   | <b>Memory Space</b><br>Wird eine Eins (1) geschrieben, kann das Gerät auf Memory Space-Zugriffe antworten.<br>Das Schreiben einer Null (0) verhindert, dass das Gerät auf Memory Space-Zugriffe antwortet.                                                    | Ja    | Ja        | 0                    |

| 2   | <b>Bus Master Enable</b><br>Wird eine Eins (1) geschrieben, verhält sich das Gerät wie ein Bus-Master (erforderlich für DMA und zum Senden von MSI/MSI-X-Interrupts)<br>Das Schreiben einer Null (0) verhindert, dass das Gerät Bus-Master-Zugriffe vornimmt. | Ja    | Ja        | 0                    |

| 3   | <b>Special Cycle Enable</b><br>Gilt nicht für PCI Express                                                                                                                                                                                                     | Ja    | Nein      | 0                    |

| 4   | <b>Memory Write and Invalidate</b><br>Gilt nicht für PCI Express                                                                                                                                                                                              | Ja    | Nein      | 0                    |

| 5   | <b>VGA Palette Snoop</b><br>Gilt nicht für PCI Express                                                                                                                                                                                                        | Ja    | Nein      | 0                    |

| 6   | <b>Parity Error Response</b><br>Meldet PCIe fehlerhaften Abschluss eines TLP (poisoned completion), wenn im PCI Status Register aktiviert (1).                                                                                                                | Ja    | Ja        | 0                    |

| 7   | <b>Wait Cycle Control</b><br>Gilt nicht für PCI Express                                                                                                                                                                                                       | Ja    | Nein      | 0                    |

| 8   | <b>SERR# Enable</b><br>Meldet PCIe Fatal und Non-fatal Errors, wenn aktiviert (1)                                                                                                                                                                             | Ja    | Ja        | 0                    |

| 9   | <b>Fast Back-to-Back Transaction Enable</b><br>Gilt nicht für PCI Express                                                                                                                                                                                     | Ja    | Nein      | 0                    |

| Bit   | Beschreibung                                                                                                                                                                                                                                                                       | Lesen | Schreiben | Wert nach PCI Reset* |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 10    | <b>Interrupt Disable</b><br>Wenn gesetzt (1), wird das Senden von Legacy-Interrupt-Meldungen (INTA#) durch die <i>ibaFOB-R</i> -Karte deaktiviert.<br>Dieses Bit hat keinen Einfluss auf MSI/MSI-X-Interrupts. Wenn gelöscht (0), werden INTA#-Interrupt-Meldungen normal erzeugt. | Ja    | Ja        | 0                    |

| 15:11 | <b>Reserviert</b>                                                                                                                                                                                                                                                                  | Ja    | Nein      | 0                    |

\*Hinweis: Dieses Register wird wahrscheinlich von der Systemsoftware während des Systemstartvorgangs geändert (z. B. 0x0106).

### PCI Status Register (Offset 0x06)

| Bit  | Beschreibung                                                                                                                                                                                                                                       | Lesen | Schreiben | Wert nach PCI Reset |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 2:0  | <b>Reserviert</b>                                                                                                                                                                                                                                  | Ja    | Nein      | 0x0                 |

| 3    | <b>Interrupt Status</b><br>Wird von der <i>ibaFOB-R</i> -Karte gesetzt, wenn die Funktion normalerweise einen Interrupt-Pin aktivieren würde, unabhängig vom Zustand des Interrupt-Disable-Bits.                                                   | Ja    | Nein      | 0                   |

| 4    | <b>New Capabilities Functions Support</b><br>Fest verdrahtet mit einer (1). Die <i>ibaFOB-R</i> -Karte implementiert eine Capabilities-Liste.                                                                                                      | Ja    | Nein      | 1                   |

| 5    | <b>66 MHz Capable</b><br>Gilt nicht für PCI Express                                                                                                                                                                                                | Ja    | Nein      | 0                   |

| 6    | <b>Reserviert</b>                                                                                                                                                                                                                                  | Ja    | Nein      | 0                   |

| 7    | <b>Fast Back-to-Back Capable</b><br>Gilt nicht für PCI Express                                                                                                                                                                                     | Ja    | Nein      | 0                   |

| 8    | <b>Master Data Parity Error</b><br>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i> -Karte einen fehlerhaften Abschluss (poisoned completion) erkannt hat, aber nur, wenn das Parity Error Response Bit im Command Register gesetzt ist. | Ja    | Ja/Clr    | 0                   |

| 10:9 | <b>DEVSEL# Timing</b><br>Gilt nicht für PCI Express                                                                                                                                                                                                | Ja    | Nein      | 0                   |

| Bit | Beschreibung                                                                                                                                                                                                                                                                                                | Lesen | Schreiben | Wert nach PCI Reset |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 11  | <p><b>Signaled Target Abort</b></p> <p>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i>-Karte einen Completer Abort signalisiert hat.</p> <p>Das Schreiben einer Eins (1) setzt dieses Bit auf Null (0) zurück.</p>                                                                               | Ja    | Ja/Clr    | 0                   |

| 12  | <p><b>Received Target Abort</b></p> <p>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i>-Karte eine Completer Abort-Antwort erhalten hat.</p> <p>Das Schreiben einer Eins (1) setzt dieses Bit auf Null (0) zurück.</p>                                                                            | Ja    | Ja/Clr    | 0                   |

| 13  | <p><b>Received Master Abort</b></p> <p>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i>-Karte eine Unsupported Request-Antwort erhalten hat.</p> <p>Das Schreiben einer Eins (1) setzt dieses Bit auf Null (0) zurück.</p>                                                                        | Ja    | Ja/Clr    | 0                   |

| 14  | <p><b>Signaled Signal System Error</b></p> <p>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i>-Karte eine ERR_FATAL- oder ERR_NONFATAL-Meldung gesendet hat, wenn das SERR#-Enable im Command Register gesetzt ist.</p> <p>Das Schreiben einer Eins (1) setzt dieses Bit auf Null (0) zurück.</p> | Ja    | Ja/Clr    | 0                   |

| 15  | <p><b>Detected Parity Error</b></p> <p>Wenn gesetzt (1), wird angezeigt, dass die <i>ibaFOB-R</i>-Karte ein fehlerhaftes (poisoned) TLP erkannt hat, unabhängig vom Status des Parity Error Response Bits im Command Register.</p> <p>Das Schreiben einer Eins (1) setzt dieses Bit auf Null (0) zurück</p> | Ja    | Ja/Clr    |                     |

### PCI Revision ID Register (Offset 0x08)

| Bit | Beschreibung                                               | Lesen | Schreiben | Wert nach PCI Reset |

|-----|------------------------------------------------------------|-------|-----------|---------------------|

| 7:0 | <p><b>Revision ID</b></p> <p>Revisionsnummer der Karte</p> | Ja    | Nein      | Aktuelle Rev#       |

### PCI Class Code Register (Offset 0x09)

| Bit                                                                                                                                      | Beschreibung                                                     | Lesen | Schreiben | Wert nach PCI Reset |

|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|-----------|---------------------|

| 7:0                                                                                                                                      | <b>Register Level Programming Interface.</b><br>Nicht definiert. | Ja    | Nein      | 0x0                 |

| 15:8                                                                                                                                     | <b>Subclass Code</b>                                             | Ja    | Nein      | 0x80                |

| 23:16                                                                                                                                    | <b>Base Class Code</b>                                           | Ja    | Nein      | 0x02                |

| Der Base Class Code von 0x02 entspricht dem Network Controller. Der Subclass Code von 0x80 entspricht einem anderen Netzwerk-Controller. |                                                                  |       |           |                     |

### PCI Header Type Register (Offset 0x0E)

| Bit | Beschreibung                                                                     | Lesen | Schreiben | Wert nach PCI Reset |

|-----|----------------------------------------------------------------------------------|-------|-----------|---------------------|

| 6:0 | <b>Configuration Layout Type</b><br><br>Null (0) zeigt ein Endpunktgerät an      | Ja    | Nein      | 0x0                 |

| 7   | <b>Header-Typ</b><br><br>Null (0) zeigt ein Gerät mit einer einzigen Funktion an | Ja    | Nein      | 0x0                 |

PCI Base Address Register 0 enthält die Startadresse für den speicherbezogenen Zugriff auf die Local Configuration Register. Der Wert in diesem Register wird durch das System-BIOS konfiguriert.

### PCI Base Address Register 0 (Offset 0x10) [Local Configuration Register]

| Bit | Beschreibung                                                                                            | Lesen | Schreiben | *Wert nach PCI Reset |

|-----|---------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 0   | <b>Memory Space Indicator</b><br><br>0 zeigt an, dass das Register in den Memory Space abgebildet wird. | Ja    | Nein      | 0                    |

| 2:1 | <b>Register Location</b><br><br>00 - An beliebiger Stelle im 32-Bit-Speicheradressraum speichern        | Ja    | Nein      | 00                   |

| 3   | <b>Prefetchable Indicator</b><br><br>0 bedeutet kein Prefetching                                        | Ja    | Nein      | 0                    |

| 8:4 | <b>Memory Base Address</b><br><br>Festcodiert auf 0x0, um eine Größe von 512 Bytes anzugeben            | Ja    | Nein      | 0x0                  |

| Bit  | Beschreibung                                                                                           | Lesen | Schreiben | *Wert nach PCI Reset |

|------|--------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 31:9 | <b>Memory Base Address</b><br>Memory Base Address für den Zugriff auf die Local Configuration Register | Ja    | Ja        | 0x0                  |

\*Hinweis: Dieses Register wird vom System-BIOS während des Bootvorgangs des Systems geändert.

Das PCI Base Address Register 1 wird in der *ibaFOB-R*-Karte nicht verwendet.

PCI Base Address Register 2 enthält die Startadresse für den speicherbezogenen Zugriff auf die RFM Control and Status-Register. Der Wert in diesem Register wird durch das System-BIOS konfiguriert.

#### PCI Base Address Register 2 (Offset 0x18) [RFM Control and Status]

| Bit  | Beschreibung                                                                                          | Lesen | Schreiben | *Wert nach PCI Reset |

|------|-------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 0    | <b>Memory Space Indicator</b><br>0 zeigt an, dass das Register in den Memory Space abgebildet wird.   | Ja    | Nein      | 0                    |

| 2:1  | <b>Register Location</b><br>00 - An beliebiger Stelle im 32-Bit-Speicheradressraum speichern          | Ja    | Nein      | 00                   |

| 3    | <b>Prefetchable Indicator</b><br>0 bedeutet kein Prefetching                                          | Ja    | Nein      | 0                    |

| 6:4  | <b>Memory Base Address</b><br>Festcodiert auf 0x0, um eine Größe von 128 Bytes anzugeben              | Ja    | Nein      | 0x0                  |

| 31:7 | <b>Memory Base Address</b><br>Memory Base Address für den Zugriff auf RFM Control und Status Register | Ja    | Ja        | 0x0                  |

\*Hinweis: Dieses Register wird vom System-BIOS während des Bootvorgangs des Systems geändert.

PCI Base Address Register 3 enthält die Startadresse für den speicherbezogenen Zugriff auf das Reflective Memory RAM. Der Wert in diesem Register wird durch das System-BIOS konfiguriert. Der Wert ist abhängig von den Einstellungen der S1-Schalterpositionen 3 und 4. Der Adress-Offset-Bereich ist:

- 0x0 bis 0x01FFFFFF für die Einstellung des 2-MB-Fensters

- 0x0 bis 0x0FFFFFF für die Einstellung des 16-MB-Fensters

- 0x0 bis 0x3FFFFFF für die Einstellung des 64-MB-Fensters

- 0x0 bis 0xFFFFFFFF für 256 MB, wenn die Einstellung des Fensters mit S1 deaktiviert wird

#### PCI Base Address Register 3 (Offset 0x1C) [Reflective Memory RAM]

| Bit  | Beschreibung                                                                                                                                                       | Lesen | Schreiben | *Wert nach PCI Reset |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 0    | <b>Memory Space Indicator</b><br>0 zeigt an, dass das Register in den Memory Space abgebildet wird.                                                                | Ja    | Nein      | 0                    |

| 2:1  | <b>Register Location</b><br>00 - An beliebiger Stelle im 32-Bit-Speicheradressraum speichern                                                                       | Ja    | Nein      | 00                   |

| 3    | <b>Prefetchable Indicator</b><br>0 bedeutet kein Prefetching                                                                                                       | Ja    | Nein      | 0                    |

| 31:4 | <b>Memory Base Address.</b><br>Memory Base Address für den Zugriff auf das Reflective Memory RAM<br>(Größe abhängig von der Fenstereinstellung wie oben erläutert) | Ja    | Ja        | 0x0                  |

\*Hinweis: Dieses Register wird vom System-BIOS während des Bootvorgangs des Systems geändert.

Die PCI Base Address Register 4 und 5 werden in der *ibaFOB-R*-Karte nicht verwendet.

#### PCI Subsystem Vendor ID Register (Offset 0x2C)

| Bit  | Beschreibung                        | Lesen | Schreiben | Wert nach PCI Reset |

|------|-------------------------------------|-------|-----------|---------------------|

| 15:0 | Subsystem Vendor ID (Hersteller-ID) | Ja    | Nein      | 0x167F<br>= iba AG  |

#### PCI Subsystem ID Register (Offset 0x2E)

| Bit  | Beschreibung | Lesen | Schreiben | Wert nach PCI Reset |

|------|--------------|-------|-----------|---------------------|

| 15:0 | Subsystem ID | Ja    | Nein      | 0x5565              |

**PCI Capabilities Pointer Register (Offset 0x34)**

| Bit | Beschreibung                                                                                                                              | Lesen | Schreiben | Wert nach PCI Reset |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 7:0 | <b>Capabilities Pointer</b><br>Offset im PCI-Konfigurationsraum für die Position des ersten Eintrags in der PCI Capabilities Linked List. | Ja    | Nein      | 0x40                |

**PCI Interrupt Line (Offset 0x3C)**

| Bit | Beschreibung                                                                                                                                                                                                       | Lesen | Schreiben | *Wert nach PCI Reset |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|----------------------|

| 7:0 | <b>Interrupt Line Routing Value</b><br>Wert, der vom Betriebssystem verwendet wird, um anzugeben, mit welchem Eingang des System-Interrupt-Controllers die (virtuelle) Interrupt-Leitung des Geräts verbunden ist. | Ja    | Ja        | 0x0                  |

\*Hinweis Dieses Register wird vom System-BIOS während des Bootvorgangs des Systems geändert.

**PCI Interrupt Pin (Offset 0x3D)**

| Bit | Beschreibung                                                                                                                                                                        | Lesen | Schreiben | Wert nach PCI Reset |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 7:0 | <b>Interrupt Pin Register</b><br>Gibt an, welchen Legacy-Interrupt-Pin das Gerät verwendet.<br>1 = INTA# (ibaFOB-R verwendet nur INTA# oder nachrichtenbezogene MSI(-X)-Interrupts) | Ja    | Nein      | 0x1                 |

Die *ibaFOB-R*-Karte unterstützt die folgenden 4 standardisierten PCI Capability-Strukturen.

Im Allgemeinen werden diese Register von der Systemsoftware verwaltet.

**Capability-Strukturen**

| PCI-Konfiguration Speicheradresse | Capability ID | Beschreibung                                             |

|-----------------------------------|---------------|----------------------------------------------------------|

| 0x40...0x47                       | 0x01          | Die Power Management Capability-Struktur                 |

| 0x48...0x4F                       | 0x05          | The MSI (Message Signaled Interrupt) Capability-Struktur |

| 0x60...0x9B                       | 0x10          | Die PCI Express Capability-Struktur                      |

| 0x9C...0xA7                       | 0x11          | Die MSI-X (erweiterte MSI) Capability-Struktur           |

**Tipp**

Ausführlichere Informationen über die verschiedenen Capability-Strukturen in PCI-Geräten finden Sie in der PCI Local Bus Specification, die von der PCI-SIG (PCI Special Interest Group) gepflegt wird. Die PCI Local Bus Specification beschreibt die Standards und Protokolle für PCI-Geräte, einschließlich der Struktur und Verwendung von Capability-Strukturen.

---

### 10.8.2 Local Configuration Register

Auf die Local Configuration Register kann unter der Adresse zugegriffen werden, die durch den Wert im Base Address Register 0 angegeben ist. Die Offsets sind im Folgenden aufgeführt.

#### Local Configuration und DMA Control Register

| Offset ab<br>Base Address | Registername                          | Beschreibbar |

|---------------------------|---------------------------------------|--------------|

| 0x00- 0x67                | <b>Reserviert</b>                     | N/A          |

| 0x68                      | Interrupt Control and Status (INTCSR) | Ja           |

| 0x6C- 0x83                | <b>Reserviert</b>                     | N/A          |

| 0x84                      | DMA PCI Address                       | Ja           |

| 0x88                      | DMA RFM Address                       | Ja           |

| 0x8C                      | DMA Transfer Size                     | Ja           |

| 0x90                      | DMA Direction                         | Ja           |

| 0x94- 0xA7                | <b>Reserviert</b>                     | N/A          |

| 0xA8                      | DMA Control and Status (DMACSR)       | Ja           |

| 0xAC- 0xB3                | <b>Reserviert</b>                     | N/A          |

| 0xB4                      | DMA PCI Upper Address                 | Ja           |

| 0xB8- 0xEF                | <b>Reserviert</b>                     | N/A          |

| 0xF0                      | RFM Window Mask                       | Nein         |

| 0xF4                      | RFM Window Base Address               | Ja           |

| 0xF8- 0xFF                | <b>Reserviert</b>                     | N/A          |

### Interrupt Control und Status Register [BAR0.0x68]

Hinweis: nur relevante Bits werden beschrieben, andere Registerbits sind reserviert (mit Null beschreiben).

| Bit | Beschreibung                                                                                                                                                                                         | Lesen | Schreiben | Wert nach PCI Reset |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 8   | <b>PCI Interrupt Enable</b><br><br>Funktioniert als globale Interrupt-Aktivierung. Das Bit muss gesetzt sein, um PCI-Interrupts zu aktivieren.                                                       | Ja    | Ja        | 1                   |

| 11  | <b>Local Interrupt Enable</b><br><br>Aktiviert die lokalen Interrupt-Quellen (RFM-Interrupts), um einen PCI-Interrupt zu erzeugen.                                                                   | Ja    | Ja        | 0                   |

| 15  | <b>Local Interrupt Active</b><br><br>Wenn gesetzt (1), ist der Local Interrupt aktiv.                                                                                                                | Ja    | Nein      | 0                   |

| 18  | <b>DMA Interrupt Enable</b><br><br>Aktiviert den DMA-Interrupt, um einen PCI-Interrupt zu erzeugen.<br><br>Das Schreiben einer Null (0) deaktiviert den DMA-Interrupt und löscht auch den Interrupt. | Ja    | Ja        | 0                   |

| 21  | <b>DMA Interrupt Active</b><br><br>Wenn gesetzt (1), ist der DMA-Interrupt aktiv (DMA-Übertragung ist beendet).                                                                                      | Ja    | Nein      | 0                   |

### DMA PCI Address Register [BAR0.0x84]

| Bit  | Beschreibung                                                                                                                                                                                                                                                                                                 | Lesen | Schreiben | Wert nach PCI Reset |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|---------------------|

| 31:0 | <b>DMA PCI Address Register</b><br><br>Zeigt an, von wo aus im PCI-Speicherbereich DMA-Übertragungen (Lesen oder Schreiben) beginnen.<br><br>Die Adresse kann an einer beliebigen Bytegrenze angeordnet werden.<br><br>Hinweis: Das Register BAR0.0xB4 muss für 32-Bit-PCI-Adressen auf Null gesetzt werden. | Ja    | Ja        | 0                   |

**DMA RFM Address Register [BAR0.0x88]**

| Bit   | Beschreibung                                                                                                                                                                                                          | Lesen | Schreiben | Wert nach PCI Reset |